Week-9 @RTEMS-GSoC-2025

Published on 11 Aug 2025

Overview

This week, I completed the following tasks :

- Debugging and investigating why TAP interface is not created in SIS for GRETH lwIP driver

- Working on solving the buffer descriptor issue as told by mentors

Work completed this week

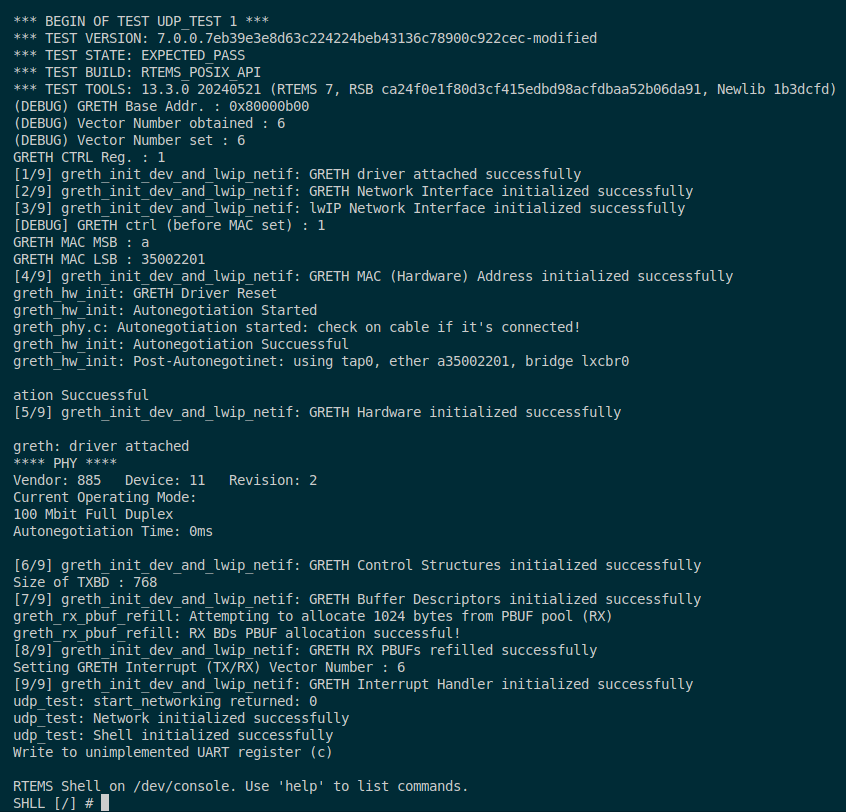

- Debugging and investigating why TAP interface is not created in SIS for GRETH lwIP driver

- The TAP inetrface is created in SIS when the GRETH Control Register’s

CTRL_RE(Receive Enable) bit is set and MAC Address is not previously assigned. - However, in my code previously, I was setting the Hardware Address much before setting

CTRL_REflag, due to which there was hinderance in creation of tap interface. SO, shifting Hardware Address Initialization before settingCTRL_REflag of GRETH Control Register solved this issue!

- The TAP inetrface is created in SIS when the GRETH Control Register’s

- Buffer Descriptor Structure and Alignment :

- The Buffer descriptors in RTEMS SIS GRETH Simulation were aligned to

BASE_PNT = 0x400, while the buffer descriptors in GRETH lwIP at this time were aligned to a smaller value . - But GRETH requires a 10 bit i.e. 1kB alignment for descriptors, and each descriptor has to be 8 bytes wide, which was also confirmed from GRETH Legacy Driver code.

- For non-gigabit mode the descriptors must be aligned to the size of descriptor table as obtained from NRD field from Status register, and for gigabit version, it has to be 1kB aligned.

- So I worked on redesigning the Descriptor structure and its proper usage throughout the code.

- The Buffer descriptors in RTEMS SIS GRETH Simulation were aligned to

Plans for next week

- Work on gettig expected results from GRETH lwIP driver transmission mechanism

- Start with reception mechanism code atleast to some extent

Blogs during GSoC-2025 period at RTEMS for the project - Providing SPARC GRETH Network Drivers for lwIP

Blogs during GSoC-2025 period at RTEMS for the project - Providing SPARC GRETH Network Drivers for lwIP